Des puces sobres qui calculent « dans la mémoire »

⏱ 5 minL’idée de rapprocher calcul et mémoire, pour gagner en puissance et en sobriété, est ancienne, mais pas très soluble dans le paysage industriel actuel. Diverses pistes sont explorées pour l’appliquer, en bousculant un peu les filières technologiques, et en faisant appel à de nouveaux types de mémoires.

C’est l’un des paradoxes de l’informatique actuelle. On croit que nos ordinateurs calculent à plein temps, en fait ce qu’ils font surtout, c’est transférer des données. Les processeurs attendent chroniquement des données en provenance de la mémoire centrale, laquelle attend souvent des informations issues des mémoires de stockage. C’est pourquoi on a inventé ces « mémoires caches », plus petites mais plus rapides, contenant localement des copies des données les plus utilisées. Mais il y a des limites à leur taille, et il faut toujours attendre les données moins fréquemment utilisées.

Énorme gâchis énergétique

Pire, ces transferts incessants entre mémoires et unités de calcul sont à l’origine d’un énorme gâchis énergétique. « L’accès aux données représente l’essentiel de la consommation électrique de nos ordinateurs, indique Elisa Vianello, responsable du programme IA embarquée au CEA-Leti. On a estimé que l’accès à l’information représente 90 % de la consommation électrique de nos ordinateurs. »

Voila pourquoi l’idée de rapprocher le calcul de la mémoire est dans l’air depuis quelque temps déjà. Le concept de « Processing in Memory » (PIM) est un serpent de mer. Une tentative précoce souvent citée est le projet IRAM (pour « Intelligent Random Access Memory ») de l’Université de Californie, à Berkeley, qui a tenté, entre 1996 et 2004, de réunir processeur et mémoire sur une puce… sans parvenir à convaincre l’industrie.

Mais plus récemment, les initiatives se sont multipliées, empruntant des voies diverses. On distingue désormais le « Near-Memory Computing » et le « In-Memory Computing ». Car la première question posée est : jusqu’où faut-il rapprocher la mémoire du calcul ? « On a montré qu’en comparaison du coût énergétique d’une addition, l’accès aux données coûte 60 fois plus si elles sont localisées dans la même puce et 3 500 fois si elles viennent de l’extérieur », assure Elisa Vianello.

Mémoire et processeur sur une même puce

Une première étape, à l’évidence, consiste à intégrer sur une même puce processeur et mémoire. Mais c’est plus facile à dire qu’à faire, explique Fabrice Devaux, le directeur technique de la start-up uPmem qui a relevé le pari : « Les filières technologiques utilisées aujourd’hui pour réaliser les processeurs et les mémoires sont très éloignées l’une de l’autre. » Une divergence essentielle porte sur le nombre de niveaux de métallisation empilés dans le « back end of line » (BEOL), au-dessus des premières couches où sont gravés les transistors, le « front end of line » (FEOL). « Pour connecter entre eux les transistors d’un processeur, poursuit Fabrice Devaux, on empile typiquement douze niveaux de métallisation, parfois jusqu’à seize ou dix-huit. Alors que pour une puce de mémoire DRAM, dont la géométrie est bien plus régulière, on se contente de trois ou quatre niveaux de métallisation. » Ce qui a un impact majeur sur leur prix de revient.

On sait réaliser de la mémoire en technologie processeur. Il s’agit de la SRAM (Static Random Access Memory), qui fait appel à six transistors au moins par bit. Beaucoup plus rapide que la DRAM, elle est aussi nettement moins dense. Elle permet donc de réaliser des caches mémoire et des mémoires locales de taille modeste, mais ne peut offrir des capacités comparables à celle des puces DRAM.

Commercialisation de barrettes mémoire

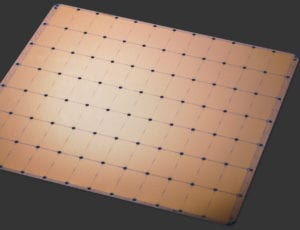

Pourquoi ne pas faire l’inverse, graver des processeurs dans la technologie des mémoires DRAM ? C’est ce que uPmem a tenté et réussi. Bien sûr, un processeur redessiné pour une filière qui ne propose que peu de niveaux de métallisation occupe plus de silicium pour des performances moindres. « Nous avons conçu un processeur en technologie DRAM, certes d’une puissance modeste, mais nous avons réussi à en installer huit sur une puce mémoire de 4 gigabits, explique Fabrice Devaux. Sur notre puce, ces cœurs occupent environ un tiers de la surface totale de silicium. »

Aujourd’hui, la start-up ne commercialise pas sa puce de mémoire nue, mais des barrettes mémoire DDR4, équipées de 16 puces, pour une capacité totale de 8 Go. « Elles sont totalement compatibles avec les PC actuels et peuvent remplacer des barrettes de mémoire classiques, mais elles contiennent en plus 128 processeurs, indique Fabrice Devaux. Sur une configuration musclée typique, on installe par exemple vingt barrettes uPmem, plus quatre barrettes normales, pour obtenir une capacité mémoire totale de 192 Go, dont 160 Go dotés de 2 560 cœurs. »

Génomique et bases de données

Il est encore tôt pour savoir quelles applications tireront le meilleur parti de cette mémoire DRAM qui calcule. Il semble qu’elle soit très adaptée à certains problèmes de génomique et à la gestion de bases de données. D’autres applications d’analyse de données sauront sans doute exploiter son potentiel, mais il n’est pas certain que l’apprentissage profond, par exemple, y trouve son compte.

Au CEA-Leti, Elisa Vianello travaille sur des hypothèses diamétralement opposées. Spécialiste des nouvelles technologies de mémoire non-volatile, elle n’envisage pas seulement de rapprocher le calcul de la mémoire, ou l’inverse, mais aussi de presque fusionner les deux. « Ces technologies de mémoire présentent l’avantage de pouvoir être gravées dans les dernières couches des puces, ce que l’on appelle le « back end of line« , où se trouvent les différents niveaux de métallisation qui interconnectent les transistors et autres composants électroniques élémentaires. La mémoire peut donc être placée à la verticale des unités de calcul. »

Préserver le contenu sans consommer d’énergie

Ces nouvelles technologies de mémoire ont en commun d’être non-volatiles : leur contenu ne dépend pas d’une alimentation électrique. Elles préservent leur contenu sans consommer aucune énergie. Pour la plupart, elles promettent à terme des temps d’accès de l’ordre de celui des SRAM pour une densité proche de celle des DRAM. « Les pistes technologiques sont nombreuses, précise Elisa Vianello. La mémoire à changement de phase (PCRAM ou Phase Change Random-Access Memory) est sur les rangs depuis des décennies. Les mémoires ferroélectriques sont disponibles depuis vingt ans. Plus récemment se sont développées les mémoires magnétorésistives (MRAM) et diverses variétés de mémoires résistives (RRAM). » La liste ne cesse de s’allonger.

Ces mémoires non conventionnelles permettent d’envisager de multiples manières de concrétiser ce rêve du « In-Memory Computing ». Elles permettent tout d’abord de graver des mémoires généreuses et rémanentes « sur » les processeurs, donc à une très courte distance. Cette approche est particulièrement intéressante pour réaliser des puces neuromorphiques dotées de nombreux cœurs optimisés pour les calculs des réseaux de neurones.

Stocker plus d’un bit par celllule

Mais ces nouvelles technologies de mémoire peuvent être exploitées selon des modalités plus radicalement nouvelles. Certaines mémoires résistives (RRAM), notamment, permettent de coder plus que deux états, et donc de stocker plus qu’un bit par cellule. Elisa Vianello a ainsi présenté l’année dernière un prototype réalisé en collaboration avec des chercheurs de l’université de Stanford, doté d’une mémoire RRAM dont chaque cellule code cinq états distincts, donc 2,3 bits par cellule. « Nous espérons améliorer ce résultat. Tout d’abord coder huit états distincts, donc trois bits par cellule. Et peut-être aller jusqu’à seize. » La capacité mémoire serait alors multipliée par quatre.

Ce n’est pas tout, ajoute Elisa Vianello. Avec ces technologies de mémoire, on peut réaliser des circuits réalisant très économiquement, en une seule étape, une opération arithmétique complexe et essentielle dans le calcul matriciel en général, le traitement du signal et… le fonctionnement des réseaux de neurones : le « Multiply-accumulate » (MAC). Une option radicale pour accélérer cette opération consiste à recourir au calcul analogique. « Il est facile de réaliser un circuit qui génère un courant qui est le produit d’une tension par une conductance. Et il est très facile d’additionner des courants… »

Un réseau de neurones à impulsions

Les mémoires non conventionnelles facilitent également l’émergence d’un autre paradigme futuriste : le réseau de neurones à impulsions, mimant encore un peu plus le fonctionnement des neurones biologiques. Le CEA-Leti a présenté en février dernier son prototype Spirit, qui serait « le premier réseau neuronal sur puce entièrement intégré doté d’une mémoire résistive non volatile », doté de « neurones analogiques à impulsions et de synapses résistives ».

Contrairement à ce qui se passe dans les circuits neuromorphiques traditionnels, qui recalculent cycliquement tous les paramètres du modèle, cette puce est très sobre parce qu’elle ne calcule que lorsque « quelque chose change ». Le réseau de neurones à impulsions (Spike Neural Network) ouvre un nouveau chapitre de l’intelligence artificielle.

Image de une : © uPmem