La puce neuromorphique géante de Cerebras bat tous les records

⏱ 5 minPour réaliser sa puce hébergeant 400 000 cœurs, la start-up Cerebras a concrétisé un vieux rêve, implanter sur une tranche entière de silicium un seul vaste circuit reconfigurable, à même de contourner les inéluctables défauts de gravure.

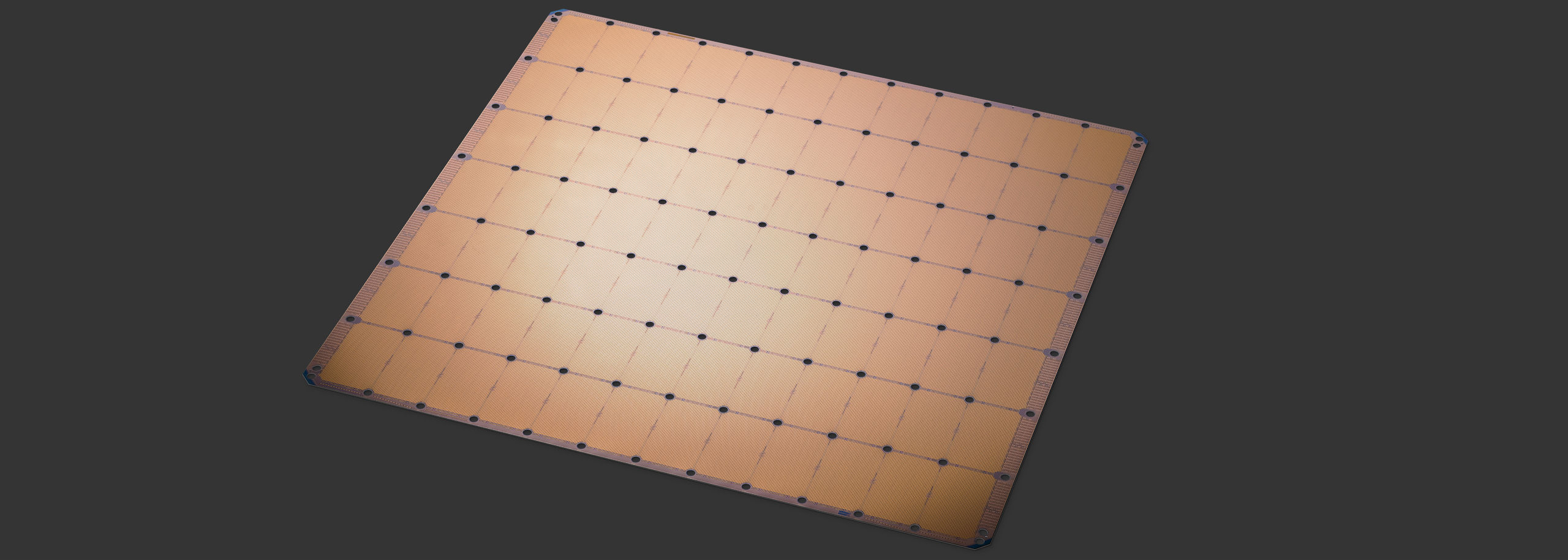

C’est en août 2019 que la petite société Cerebras, installée à Los Altos, en plein cœur de la Silicon Valley, en Californie, a présenté son « Wafer Scale Engine » (WSE) : une puce neuromorphique gigantesque (215 × 215 mm), occupant 46 225 mm2 de silicium et sur laquelle sont gravés 1 200 milliards de transistors. À titre de comparaison, la puce Ampère A100 de Nvidia, la plus grande actuellement commercialisée, comporte 54 milliards de transistors sur 826 mm2 de silicium. Et c’est un exploit.

La puce de Cerebras regroupe 400 000 cœurs qui ont accès à 18 Go de mémoire locale. Ces cœurs ne sont ni des CPU ni des GPU, mais des « Sparse Linear Algebra Compute Cores » (SLAC), des processeurs optimisés pour le type de calcul nécessaire au fonctionnement des réseaux de neurones.

Pour regrouper sur une puce 56 fois plus de transistors que Nvidia, Cerebras a concrétisé un rêve formulé dès les années 1970 : la « Wafer Scale Integration » (WSI). L’idée peut sembler triviale : puisque les puces sont gravées sur des tranches de silicium, des « wafers » de grande dimension, aujourd’hui typiquement de 30 cm de diamètre, pourquoi ne pas exploiter toute cette surface pour réaliser une seule puce surpuissante ?

La photolithographie a ses limites

Rappelons que la fabrication des circuits électroniques intégrés repose sur des techniques de photolithographie. Partant d’une mince plaque de silicium (typiquement 0,7 mm), une succession d’opérations a pour effet de creuser, oxyder, doper, déposer des couches de matériaux divers… selon un dessin très précis. Lequel est défini à chaque fois par la bonne vieille technique du pochoir. Un matériau photosensible est déposé sur le circuit, puis une image y est projetée. Après un traitement chimique, qui a pour effet de dissoudre les zones exposées à la lumière, on obtient un masque, qui définit les zones à protéger ou exposer au traitement à venir.

« Dans les années 1970, quand on gravait à l’échelle du micron, on pouvait exposer d’un coup des surfaces de 10 000 mm2 », explique Ying-Chih Yang, le directeur technique de SiPearl. Dans le cadre de la European Processor Initiative (EPI), il est l’architecte du microprocesseur destiné notamment au futur supercalculateur exascale européen. « Comme on travaillait à l’époque sur des wafers de 50, 75 ou 100 millimètres de diamètres, il était tentant d’envisager d’utiliser toute la surface pour réaliser une seule grande puce. »

Mais en cinquante ans, la finesse de gravure est passée des micromètres aux nanomètres tandis que la taille des wafers augmentait. Conséquence : on est incapable de projeter avec la précision nécessaire des images de 30 cm de diamètre comportant des détails nanométriques. « Les techniques actuelles de photolithographie ne permettent pas de graver des puces dont la surface dépasse 800 mm2 environ, notamment à cause de limitations optiques, explique Ying-Chih Yang.

Des défauts inéluctables

Un autre obstacle s’oppose à la réalisation de puces toujours plus grandes. Un phénomène au centre des préoccupations des « fonderies » qui fabriquent les puces électroniques : malgré toutes les précautions prises, en fin de parcours leurs wafers comportent toujours quelques petits défauts. Ce n’est pas faute d’avoir organisé la chasse aux poussières, dans ces « salles blanches » dont l’atmosphère est filtrée et où le personnel est habillé comme des chirurgiens. Mais il suffit d’une infime particule mal placée pour qu’une petite zone d’un wafer soit défectueuse.

C’est pourquoi un paramètre essentiel, surveillé dans toutes les fonderies, est le « yield », le rendement. La proportion de puces fonctionnelles à l’issue du processus de fabrication. Si on déplore par exemple vingt défauts en moyenne sur chaque wafer où sont gravées mille petites puces, on obtient statistiquement environ 98 % de puces fonctionnelles. Mais si on grave cent grosses puces, le ratio sera de l’ordre de 80 %. Et si ce wafer ne comportait qu’un seul circuit, la probabilité qu’il ne soit affligé d’aucun défaut et soit donc totalement fonctionnel est très proche de zéro. Et le rendement quasi nul.

Contourner les éléments non fonctionnels

Bien sûr, tout est mis en œuvre pour réduire le nombre de défauts, mais aucun fabricant n’espère être capable de produire une proportion utile de wafers sans aucune imperfection. Mais alors, comment Cerebras a bien pu faire réaliser ses puces géantes chez TSMC, le célèbre fondeur taïwanais, qui est certes l’un des meilleurs, mais ne prétend pas faire des miracles ? C’est un principe central de la Wafer Scale Integration : la conception même de cette puce intègre le fait que certaines régions ne fonctionneront pas. Son dessin est très répétitif, redondant, et des mécanismes sont prévus pour isoler et contourner les processeurs non fonctionnels.

D’ailleurs, si le WSE de Cerebras occupe bien l’essentiel de la surface d’un wafer de 300 mm de diamètre, plus précisément un carré de 215 mm de côté, c’est en fait l’équivalent de 84 puces qui y sont gravées : on distingue sur les photos sept rangées de douze blocs. Ce qui ressemble furieusement à un wafer sur lequel on aurait fabriqué 84 puces d’une taille comparable à celle des plus puissantes proposées par Nvidia et d’autres. Mais dans l’intervalle entre ces blocs, là où d’habitude passe la scie qui découpe les wafers en puces, Cerebras a trouvé une solution pour graver une interconnexion permettant à chacune de ses 84 puces de communiquer avec ses voisines.

Au final, ces 84 blocs interconnectés réunissent 400 000 cœurs, interconnectés de proche en proche via un réseau maillé. Le WSE comporte, de plus, 18 Go de mémoire locale, accessible en un seul cycle d’horloge. La bande passante mémoire totale s’élèverait à neuf pétaoctets par seconde (9 000 To/s).

Le défi du packaging

Pour réaliser cet exploit, l’équipe de Cerebras a escaladé plus d’une difficulté. « La puce Cerebras consomme 15 kW d’électricité et peut donc dégager jusqu’à 15 kW de chaleur, indique Marc Duranton, expert scientifique au CEA-List. Ce qui ne va pas sans poser des problèmes de contraintes thermiques, de dilatation et donc de contraintes mécaniques. Il semble que ses concepteurs ont réussi à mettre au point une solution viable d’une part pour extraire cette chaleur du wafer à l’aide d’une plaque métallique refroidie par circulation d’eau, et d’autre part pour assurer une connexion électrique fiable malgré les déformations, notamment en faisant appel à un élastomère conducteur souple. »

Le chemin emprunté par Cerebras s’avère adapté à la fabrication d’une puce géante neuromorphique, mais n’est sans doute pas une solution généralisable à d’autres types de circuits. « Un compromis essentiel pour réaliser cette puce concerne la quantité de mémoire disponible, indique Ying-Chih Yang. En cinquante ans, l’industrie a développé des filières technologiques séparées, optimisées pour la fabrication des processeurs et de la mémoire vive. En conséquence, on ne sait pas intégrer de la mémoire avec une densité comparable à celle des puces ad-hoc sur le silicium de puces réalisées dans la technologie conçue pour les microprocesseurs. Cerebras a réussi à intégrer 18 Go de mémoire rapide sur son wafer, pour 400 000 cœurs, ce qui serait très insuffisant s’il s’agissait de cœurs destinés au calcul intensif, mais peut convenir pour des réseaux de neurones. Dans un design neuromorphique, on cherche à obtenir un débit mémoire très élevé mais on peut se contenter d’une capacité modeste. »

Une filière à mettre en place

Quelle ampleur prendra le phénomène WSI ? « Au-delà de cet exploit, estime Marc Duranton, l’avenir dépendra de la rentabilité économique de cette approche. Pour que les systèmes à base de WSI décollent, il faut bâtir tout une filière technologique, allant de la lithographie (pour assurer les connexions entre puces sur le wafer) jusqu’au packaging, en passant par les équipements de test, les systèmes de refroidissement, de nouveaux matériaux ad-hoc, et bien d’autres choses. »

Cerebras ne commercialise pas la puce WSE elle-même, mais seulement un système complet construit autour d’elle. Son prix n’est pas divulgué, mais certains observateurs l’évaluent à quelque 2 millions de dollars. Depuis l’annonce, les premiers exemplaires ont été livrés. On explore son potentiel notamment dans de grands laboratoires de recherche comme le Lawrence Livermore National Laboratory, en Californie, le Argonne National Laboratory, dans l’Illinois ou chez GlaxoSmithKline, à Londres.

En août dernier, Cerebras a indiqué qu’un prototype de deuxième génération était prêt. Alors que le premier WSE était gravé en 16 nanomètres, celui-ci est réalisé en 7 nanomètres, toujours par la fonderie taïwanaise TSMC. Le nombre de transistors passe de 1 200 à 2 600 milliards. Et de 400 000, on passe à 850 000 cœurs. De quoi faire « tourner » des réseaux de neurones gigantesques.

Image de une : © Cerebras